首頁 / 重點研發 / 前瞻半導體與智能系統 / 新興智慧記憶體與系統

新興智慧記憶體與系統

#超低能耗鐵電記憶體 #超低能耗磁電自旋-反自旋霍爾(MEISH)元件 #超低能耗記憶體內運算

願景

- 整合過去多功能磁阻式記憶體、後段製程相容鐵電記憶體、三維記憶體的開發經驗,以達到50 Mb/mm2的高密度、小於1.2 V的操作電壓,小於1 pJ的寫入能量為目標。

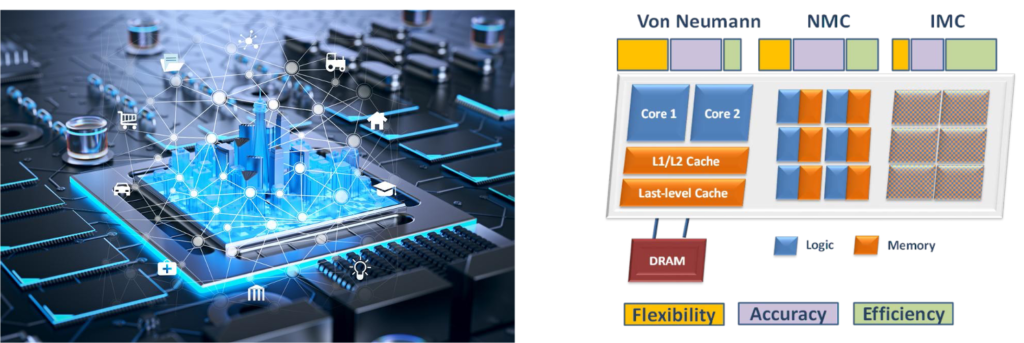

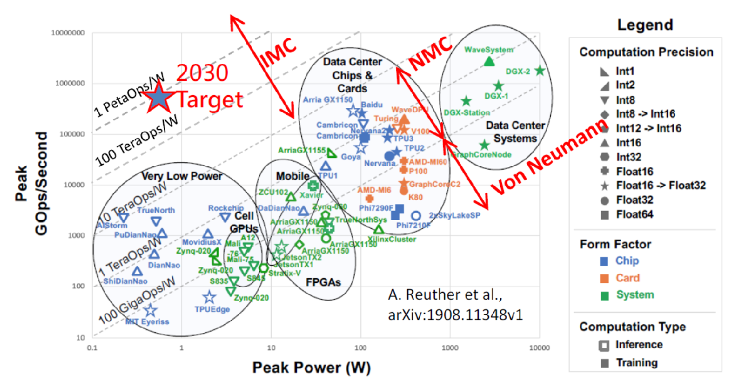

- 在當前的大數據時代,現有以處理器為本(processor centric)的架構因需極大量的數據傳輸,無論能耗或運算速度皆受到很大的限制。資訊硬體架構設計因此逐步轉向以數據為本(data centric),俾縮短運算與記憶單元間的距離並提高頻寬。放眼未來十年,人類產生的數據仍將呈指數性的高速增長,人工智慧技術的突破雖使我們有能力將龐雜數據轉化為精簡資訊,但這將需要遠超過現有運算效能的硬體方能達成。本校研究團隊將推動以數據為本之超低能耗異質運算技術突破,結合范紐曼架構、近記憶體運算(near-memory computing; NMC)暨“超范紐曼架構“之記憶體內運算(in-memory computing; IMC),以滿足不同運算任務對彈性、精確性、能效間不同的需求平衡。

關鍵議題

- 以先進邏輯後段製程相容的磁阻式記憶體與鐵電記憶體為研究重點。

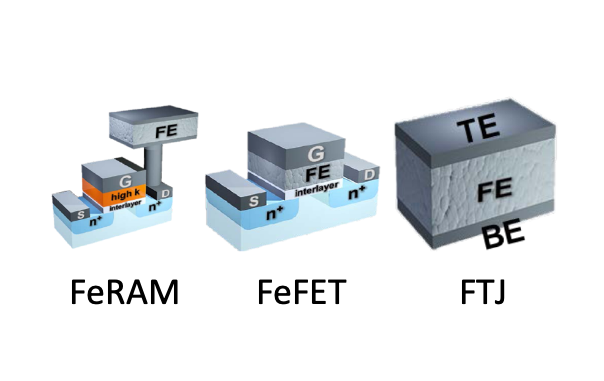

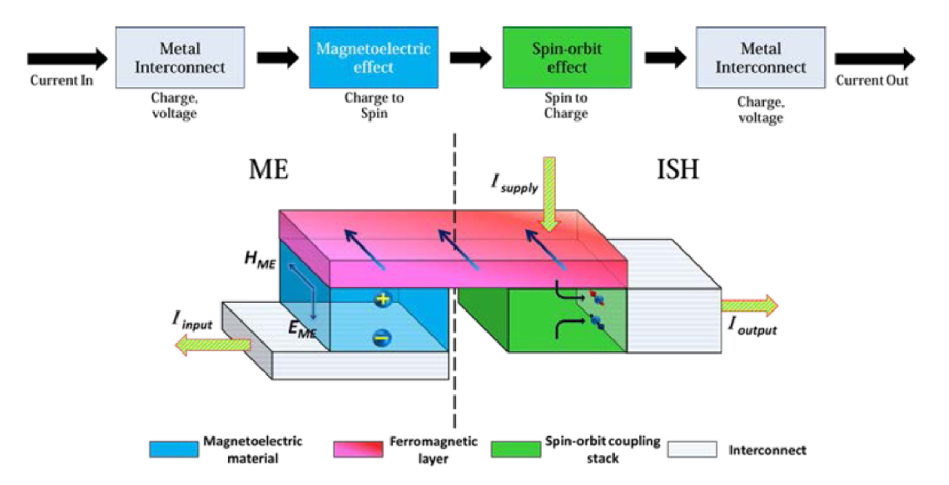

- 擁有極低操作能耗的鐵電記憶體,依賴鐵電材料在外加電場下的自發電極化儲存資訊,近年與先進邏輯相容的鐵電氧化鉿(HfO2)與氧化鉿鋯(HZO)材料被發現後,成為極受關注的議題。具有可微縮、非破壞性讀取,利於高密度三維陣列整合等優點之鐵電場效電晶體(FeFET)與鐵電穿隧接面(FTJ),以及高度微縮元件所需之新穎鐵電材料均仍有開發空間。上述兩種元件中,前者因電荷捕捉效應引起的耐受力劣化後者穿隧電流與記憶窗口過小的問題仍待解決;而超薄(<5 奈米)鐵電材料的合成仍相當困難,微縮極限不明。此外,磁電自旋-反自旋霍爾(magnetoelectric & inverse spin-Hall, MEISH)元件可以實現反向器與多數閘(majority gate),更重要的是能有效將能耗降至阿焦耳(10-18J, aJ)等級,被認為有機會成為超越CMOS 的新穎邏輯技術。MEISH 元件由兩項可微縮技術構成:磁電切換機制和自旋流轉電流之拓撲轉換讀取機制。相較於CMOS 技術,MEISH 元件有更低的切換能量(僅1/10)與切換電壓(僅1/5)、更高的邏輯密度(5倍),且其非揮發性有效降低待機功率。然而目前MEISH 僅有理論模型與尚未成熟的雛型驗證,亟需更多的研究投入。另一方面,記憶體內運算將數據儲存與運算合而為一,基本解決數據傳輸的瓶頸,於人工智慧硬體加速的潛力倍受矚目。但目前結合架構、演算法、電路、元件的記憶體內運算跨層級優化設計未臻成熟,整合先進邏輯與記憶體製程實現單晶片的技術亦尚未普及,使得記憶體內運算仍多停留在研究階段。

關鍵研究方向及技術

超低能耗鐵電記憶體

鐵電記憶體元件架構主要可歸納為三種:(1) FeRAM (ferroelectric RAM)為1T(transistor)-1C(capacitor)架構,缺點為面積受限於電容大小較無法微縮且有破壞性讀取(destructive readout)問題。破壞性讀取表示每次讀取皆須伴隨一重新寫回的動作,不但增加元件的功耗,對元件寫入次數的要求也極高;(2) FeFET (ferroelectric FET)為1T 結構,由電晶體的Vth 變化來表示儲存狀態,不但記憶體面積小且無破壞性讀取疑慮;(3) FTJ (ferroelectric tunnel junction)為簡單的兩端點結構,藉由穿隧電流大小表示儲存狀態,具微縮容易、非破壞性讀取和低電流操作等優點。在未來超低能耗鐵電記憶體應用上,為達高儲存密度且非破壞性讀取,FeFET 和FTJ 為鐵電記憶體較為可能之架構。

FeFET其結構與操作與一般電晶體相似,藉由閘極鐵電層不同的極化態來調控高/低Vth,讀取時便可得到不同的電流值,分別可當作獨立的儲存狀態。不過,寫入極化態所需施加的電場亦可能造成電荷捕捉,因而造成耐久性(endurance)衰退的問題。鐵電電偶極矩極化與介面層的捕捉電荷作用相互抵銷,將使記憶窗口(memory window)縮小。此外,為降低操作電壓和微縮電晶體尺寸以增加儲存密度,如何減薄鐵電層厚度(< 5 奈米)且保有鐵電性質與低的漏電流將是重要之挑戰。當元件尺寸微縮至數十奈米等級,新的行為也必須探討。最後,如何利用3D結構進一步提升儲存密度也需要被探索,以滿足未來對更高儲存容量之需求。

FTJ 利用電偶極矩方向改變元件能帶結構,進而造成高低阻態的穿隧電流差別,其電子穿隧的機制使得FTJ 擁有極低的電流。此外,兩端點元件也具備了可微縮性,能高密度排列並進行三維堆疊,短時間(奈秒)即可翻轉偶極矩,並擁有良好的可靠度,將有利於應用在記憶體內運算硬體上。然而,如何提高FTJ的穿隧電流則為另一關鍵挑戰。

超低能耗磁電自旋-反自旋霍爾(MEISH)元件

磁電自旋-反自旋霍爾(magnetoelectric & inverse spin-Hall)元件被認為是有機會成為超越CMOS 的一種新穎計算邏輯技術。MEISH元件由兩項可微縮技術之轉換機制構成:鐵電/磁電切換機制和自旋流轉電流之拓撲轉換機制。該元件連接電內連導線,因此為電荷/電壓驅動,產生電荷/電壓輸出。MEISH 元件由一磁電電容器、一鐵電和一自旋流轉電流轉換模組組成;相較於CMOS 技術,MEISH 元件有較低的切換能量(僅1/10 至1/30)、較低的切換電壓(僅2/5),以及提升的邏輯密度(5 倍);此外,其非揮發性可使待機功率超低。

超低能耗記憶體內運算

今日的計算機系統主要由馮紐曼(Von Neumann)架構所建立,其架構雖具有高度的彈性(flexibility),且利用浮點數運算能有非常高的精確度(accuracy),然而,因為邏輯運算能力與記憶體速度不匹配,且資料需要在頻寬不足的資料匯流排(data bus)中來回的搬動,造成不必要之等待與功率損耗,能源使用效率(energy efficiency)低,在處理大數據或極低功耗的可攜式裝置上有其應用極限。為解決此技術瓶頸,各式以資料為核心(data-centric)或稱為以記憶體為核心(memory-centric)的運算架構因應而生,近記憶體運算(near-memory computing; NMC)架構,利用高頻寬的資料匯流排連接運算與儲存單元,目前可透過嵌入式記憶體技術或3D 封裝方式實現,能在與馮紐曼架構相容度高的系統上實現更高的能效,現行的GPU與AI加速器皆是利用相似的概念。在追求極致高能效上最終的解決方案是完全或盡可能地避免資料的搬移,因此利用記憶體內儲存的資料直接進行類比運算的方式因應而生,稱之為記憶體運算(In-memory computing; IMC)。記憶體運算可以有效減少資料的搬移,並使用高度平行化的記憶體陣列結構進行高通量的運算,被認為在人工智慧加速上有高能效、高密度、高運算能力等優勢。

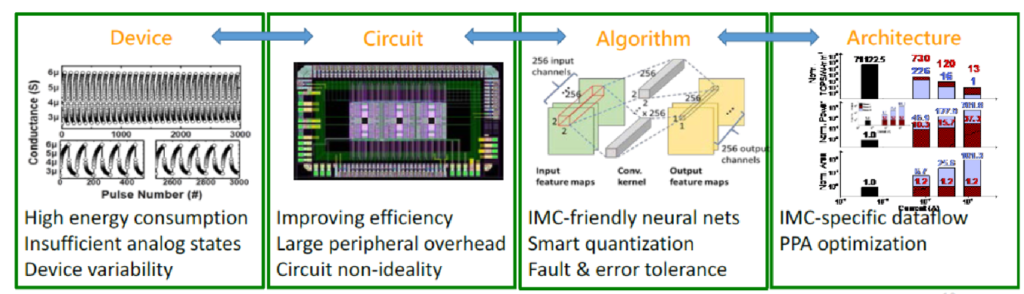

先前記憶體運算架構做法的假設是不改動演算法,尋求一個可以將演算法對應至記憶體運算的作法。這方法雖然可行,但並未考慮硬體的限制,也未能發揮硬體的好處。我們的概念是神經網路演算法較有彈性容錯空間,因此應當設計神經網路演算法與系統去適應元件與電路之先天限制,發揮元件與電路平行計算特性以加速演算法與系統計算,達成演算法-架構-電路-元件的共同最佳化。在元件端需考量如何有效下降元件運算所需的能耗、不足的類比記憶狀態、與無法避免的元件變異。在電路端需考量如何有效降低周邊電路的功耗、面積與電路的非理想與非線性的效應。在演算法端需考量如何如何實現記憶體內硬體友善的人工智慧演算法,使用最低所需的精度進行運算,並容忍元件與電路可能造成的錯誤。在架構端需考量如何最佳化整體晶片中的資料流(data flow),優化整體晶片的性能、功耗與面積(performance-power-area; PPA)。

其他相關子計畫:前瞻半導體

前瞻半導體與智能系統

為因應全球高速無線通訊(B5G/6G)、 智能物聯網、自駕車、智慧道路、與節能減碳等應用發展趨勢,本校布局毫米波/太赫茲、大頻寬、高功率、高密度與能效儲存、高能效運算(AI)、超低延遲及智慧能源管理等…

節能能源管理系統之功率元件

#極力開發碳化矽、氮化鎵、及氧化鎵等功率元件 #下世代氮化鎵功率元件與閘極驅動器 #下世代氧化鎵功率元件 成員合照 願景 根據市場分析指出,未來二十年功率元件的市場會持續成長,且對於不同的應用,在耐壓…

超高密度三維積體電路技術與二維通道材料

#世界首創單晶矽島三維堆疊積體電路技術 #世界最高HZO鐵電相(78%)技術 願景 發展次奈米世代技術節點的超高密度三維元件之架構和通道材料,將以垂直堆疊互補式電晶體(complementary FE…

下世代高頻元件與電路

#毫米波矽基米元件設計與優化 #新世代高頻射頻電路設計 #氮化鎵高頻元件與電路開發 願景 未來社會中,高速無線通信的需求將急遽增加。隨著物聯網時代的到來,各種智慧聯網應用,如智慧城市、智慧家庭、智慧交…

其他相關子計畫:智能系統

前瞻AI自駕車多模感測與融合技術

#自駕車嵌入式AI深度學習技術 #分散式輕量化在地化自動駕駛系統 #智慧道路之前瞻AI路邊站多模感測(雷達與攝影機)與融合技術 願景與特色 建立台灣開放式 ADAS/自駕車標記資料集 研發自駕車嵌入式…